Description

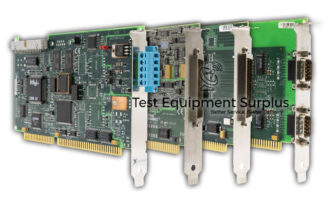

The Part Number 780561-01 corresponds to the Model PXI-7952R, which is categorized under PXI FlexRIO Baseboards. This model is equipped with 128 MB DRAM for memory requirements and operates on a Virtex 5 LX50 FPGA, ensuring high performance and reliability for demanding applications.

It is compatible with NI connector modules for FlexRIO, allowing for versatile and flexible usage across various applications. The Connector Module Interface supports Component-Level IP (CLIP), enabling easy integration and customization of the module based on specific requirements.

The Programming Interface includes LabVIEW FPGA and IP Integration Node, providing a user-friendly environment for programming and development. The device connects to the backplane through a PCI connection, ensuring high-speed data transfer and communication with the host system.

With 48 DSP slices and 1,728 Block RAM (BRAM), the PXI-7952R offers substantial processing power and memory capacity for handling complex algorithms and data-intensive applications. Additionally, it boasts 7,200 FPGA slices and 28,800 flip-flops, further enhancing its computational capabilities.

The device operates with a Default Timebase of 40 MHz, ensuring precise timing and synchronization for all operations. It also features 132 General-Purpose Channels, which can be configured as single-ended, differential, or an arrangement of both, providing exceptional flexibility in connecting and interfacing with external devices.

The PXI-7952R has reached Mature Status, as announced by National Instruments. It remains available for purchase and repairs through Apex Waves, ensuring long-term support and availability for users of this advanced and versatile module.

| Specification | Details |

|---|---|

| Part Number | 780561-01 |

| Model | PXI-7952R |

| Category | PXI FlexRIO Baseboards |

| Memory | 128 MB DRAM |

| FPGA | Virtex 5 LX50 |

| Compatibility | NI connector modules for FlexRIO |

| Connector Module Interface | Component-Level IP (CLIP) |

| Programming Interface | LabVIEW FPGA, IP Integration Node |

| Backplane Connection | PCI |

| DSP Slices | 48 |

| Block RAM (BRAM) | 1,728 |

| FPGA Slices | 7,200 |

| Flip-Flops | 28,800 |

| Default Timebase | 40 MHz |

| General-Purpose Channels | 132 (can be single-ended, differential, or an arrangement of both) |

| Mature Status | Announced by National Instruments, available for purchase and repairs by Apex Waves |